## **COMP2121: Microprocessors and** Interfacing

Interrupts

http://www.cse.unsw.edu.au/~cs2121 Lecturer: Hui Wu Term 2, 2019

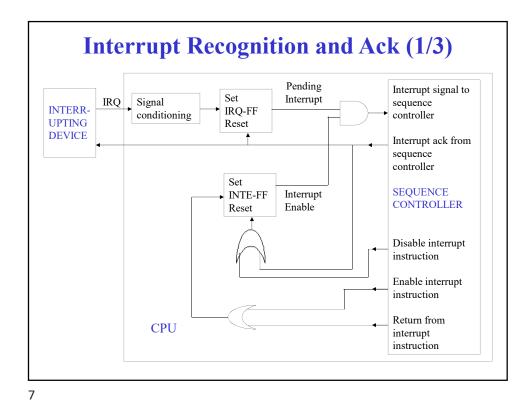

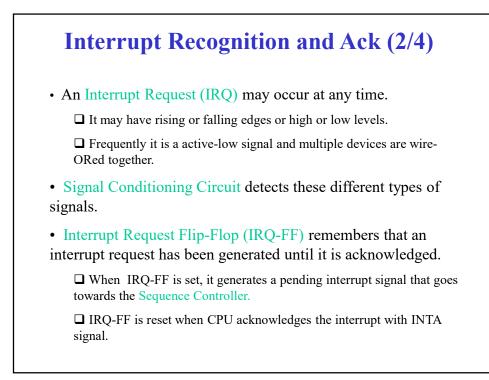

- 1. Allow for asynchronous events to occur and be recognized.

- 2. Wait for the current instruction to finish before taking care of any interrupt.

- 3. Branch to the correct interrupt handler, also called interrupt service routine, to service the interrupting device.

- 4. Return to the interrupted program at the point it was interrupted.

- 5. Allow for a variety of interrupting signals, including levels and edges.

- 6. Signal the interrupting device with an acknowledge signal when the interrupt has been recognized.

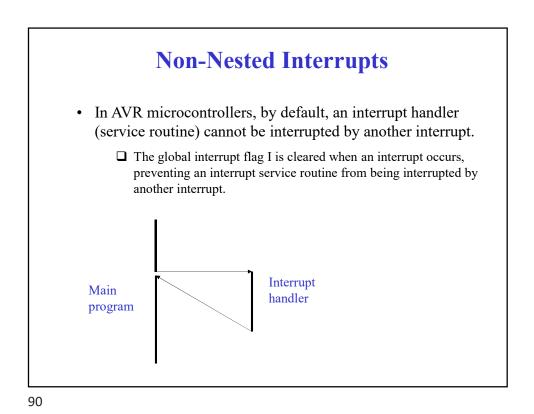

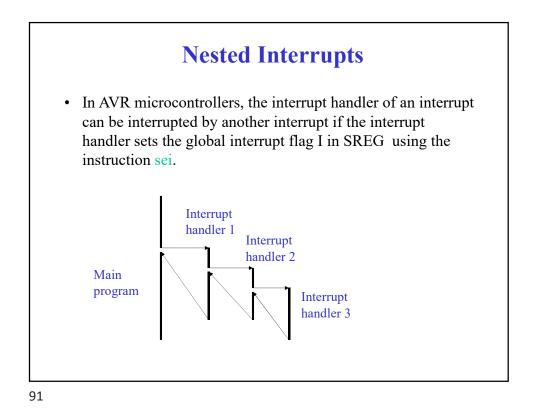

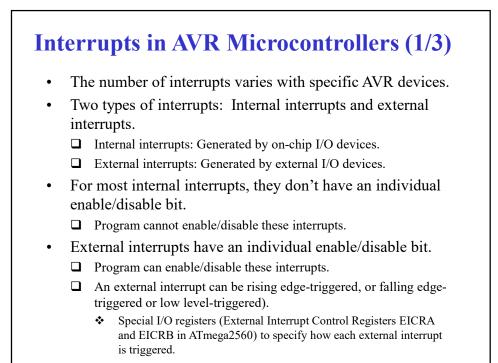

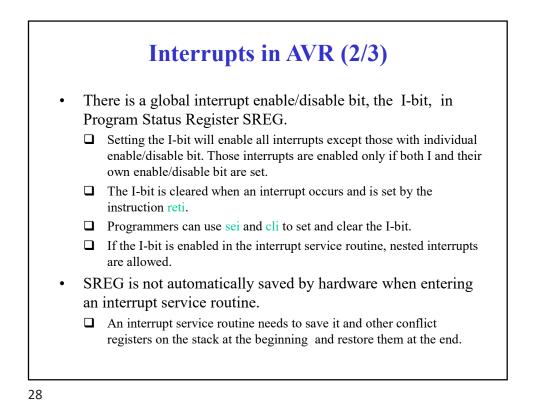

# Interrupt System Specifications (2/2) Allow programmers to selectively enable and disable all interrupts. Allow programmers to enable and disable selected interrupts. Disable further interrupts while the first is being serviced Deal with multiple sources of interrupts. Deal with multiple, simultaneous interrupts.

#### Transferring Control to Interrupt Handler

- Hardware needs to save the return address.

- $\Box$  Most processors save the return on the stack.

- ARM uses a special register, link register, to store the return address.

- Hardware may also save some registers such as program status register.

- AVR does not save any register. It is programmer's responsibility to save program status register and conflicting registers.

- The delay from the time the IRQ is generated by the interrupting device to the time the interrupt handler starts to execute is called interrupt latency.

#### **Software Interrupt**

- Software interrupt is the interrupt generated by software without a hardware-generated-IRQ.

- Software interrupt is typically used to implement system calls in OS.

- Most processors provide a special machine instruction to generate software interrupt.

- SWI in ARM.

- AVR does NOT provide a software interrupt instruction.

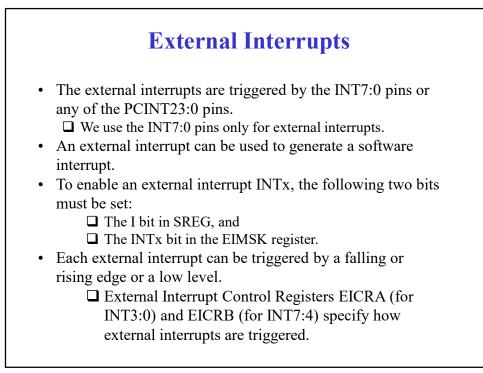

- Programmers can use External Interrupts to implement software interrupts.

□ Can be relocated.

|               | 1 - construction of the           | r            |                                                                                      |

|---------------|-----------------------------------|--------------|--------------------------------------------------------------------------------------|

| Vector<br>No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                                 |

| 1             | \$0000(1)                         | RESET        | External Pin, Power-on Reset, Brown-out Reset,<br>Watchdog Reset, and JTAG AVR Reset |

| 2             | \$0002                            | INT0         | External Interrupt Request 0                                                         |

| 3             | \$0004                            | INT1         | External Interrupt Request 1                                                         |

| 4             | \$0006                            | INT2         | External Interrupt Request 2                                                         |

| 5             | \$0008                            | INT3         | External Interrupt Request 3                                                         |

| 6             | \$000A                            | INT4         | External Interrupt Request 4                                                         |

| 7             | \$000C                            | INT5         | External Interrupt Request 5                                                         |

| 8             | \$000E                            | INT6         | External Interrupt Request 6                                                         |

| 9             | \$0010                            | INT7         | External Interrupt Request 7                                                         |

| 10            | \$0012                            | PCINT0       | Pin Change Interrupt Request 0                                                       |

| 11            | \$0014                            | PCINT1       | Pin Change Interrupt Request 1                                                       |

| 12            | \$0016 <sup>(3)</sup>             | PCINT2       | Pin Change Interrupt Request 2                                                       |

| 13            | \$0018                            | WDT          | Watchdog Time-out Interrupt                                                          |

| 14            | \$001A                            | TIMER2 COMPA | Timer/Counter2 Compare Match A                                                       |

| 15            | \$001C                            | TIMER2 COMPB | Timer/Counter2 Compare Match B                                                       |

| 16 | \$001E | TIMER2 OVF   | Timer/Counter2 Overflow        |

|----|--------|--------------|--------------------------------|

| 17 | \$0020 | TIMER1 CAPT  | Timer/Counter1 Capture Event   |

| 18 | \$0022 | TIMER1 COMPA | Timer/Counter1 Compare Match A |

| 19 | \$0024 | TIMER1 COMPB | Timer/Counter1 Compare Match B |

| 20 | \$0026 | TIMER1 COMPC | Timer/Counter1 Compare Match C |

| 21 | \$0028 | TIMER1 OVF   | Timer/Counter1 Overflow        |

| 22 | \$002A | TIMER0 COMPA | Timer/Counter0 Compare Match A |

| 23 | \$002C | TIMER0 COMPB | Timer/Counter0 Compare match B |

| 24 | \$002E | TIMER0 OVF   | Timer/Counter0 Overflow        |

| 25 | \$0030 | SPI, STC     | SPI Serial Transfer Complete   |

| 26 | \$0032 | USART0 RX    | USART0 Rx Complete             |

| 27 | \$0034 | USART0 UDRE  | USART0 Data Register Empty     |

| 28 | \$0036 | USART0 TX    | USART0 Tx Complete             |

| 29 | \$0038 | ANALOG COMP  | Analog Comparator              |

| 30 | \$003A                | ADC          | ADC Conversion Complete        |

|----|-----------------------|--------------|--------------------------------|

| 31 | \$003C                | EE READY     | EEPROM Ready                   |

| 32 | \$003E                | TIMER3 CAPT  | Timer/Counter3 Capture Event   |

| 33 | \$0040                | TIMER3 COMPA | Timer/Counter3 Compare Match A |

| 34 | \$0042                | TIMER3 COMPB | Timer/Counter3 Compare Match B |

| 35 | \$0044                | TIMER3 COMPC | Timer/Counter3 Compare Match C |

| 36 | \$0046                | TIMER3 OVF   | Timer/Counter3 Overflow        |

| 37 | \$0048                | USART1 RX    | USART1 Rx Complete             |

| 38 | \$004A                | USART1 UDRE  | USART1 Data Register Empty     |

| 39 | \$004C                | USART1 TX    | USART1 Tx Complete             |

| 40 | \$004E                | TWI          | 2-wire Serial Interface        |

| 41 | \$0050                | SPM READY    | Store Program Memory Ready     |

| 42 | \$0052 <sup>(3)</sup> | TIMER4 CAPT  | Timer/Counter4 Capture Event   |

| 43 | \$0054                | TIMER4 COMPA | Timer/Counter4 Compare Match A |

| 44 | \$0056                | TIMER4 COMPB | Timer/Counter4 Compare Match B |

| 45 | \$0058                | TIMER4 COMPC | Timer/Counter4 Compare Match C |

## Interrupt Vectors in ATmega2560 (4/4)

| 46 | \$005A                 | TIMER4 OVF   | Timer/Counter4 Overflow        |

|----|------------------------|--------------|--------------------------------|

| 47 | \$005C <sup>(3)</sup>  | TIMER5 CAPT  | Timer/Counter5 Capture Event   |

| 48 | \$005E                 | TIMER5 COMPA | Timer/Counter5 Compare Match A |

| 49 | \$0060                 | TIMER5 COMPB | Timer/Counter5 Compare Match B |

| 50 | \$0062                 | TIMER5 COMPC | Timer/Counter5 Compare Match C |

| 51 | \$0064                 | TIMER5 OVF   | Timer/Counter5 Overflow        |

| 52 | \$0066 <sup>(3)</sup>  | USART2 RX    | USART2 Rx Complete             |

| 53 | \$0068 <sup>(3)</sup>  | USART2 UDRE  | USART2 Data Register Empty     |

| 54 | \$006A <sup>(3)</sup>  | USART2 TX    | USART2 Tx Complete             |

| 55 | \$006C <sup>(3)</sup>  | USART3 RX    | USART3 Rx Complete             |

| 56 | \$006E <sup>(3))</sup> | USART3 UDRE  | USART3 Data Register Empty     |

| 57 | \$0070 <sup>(3)</sup>  | USART3 TX    | USART3 Tx Complete             |

33

## Interrupt Vectors in ATmega2560 (2/3)

| 45 | 0.0010                | TIMED: OVE   | T IO I IO II                   |

|----|-----------------------|--------------|--------------------------------|

| 15 | 0x001C                | TIMER1 OVF   | Timer/Counter1 Overflow        |

| 16 | 0x001E                | TIMERO COMP  | Timer/Counter0 Compare Match   |

| 17 | 0x0020                | TIMERO OVF   | Timer/Counter0 Overflow        |

| 18 | 0x0022                | SPI, STC     | SPI Serial Transfer Complete   |

| 19 | 0x0024                | USARTO, RX   | USARTO, Rx Complete            |

| 20 | 0x0026                | USARTO, UDRE | USARTO Data Register Empty     |

| 21 | 0x0028                | USARTO, TX   | USARTO, Tx Complete            |

| 22 | 0x002A                | ADC          | ADC Conversion Complete        |

| 23 | 0x002C                | EE READY     | EEPROM Ready                   |

| 24 | 0x002E                | ANALOG COMP  | Analog Comparator              |

| 25 | 0x0030 <sup>(3)</sup> | TIMER1 COMPC | Timer/Countre1 Compare Match C |

## Interrupt Vector Initialization in ATmega2560 (1/5)

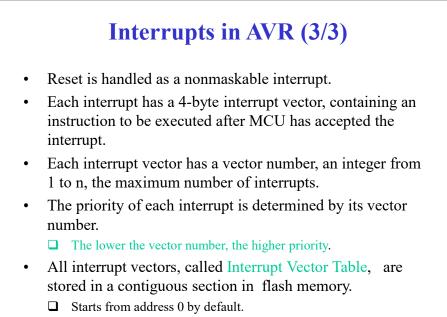

• Typically an interrupt vector contains a branch instruction (jmp) that branches to the first instruction of the interrupt handler, or reti (return from interrupt), indicating that this interrupt is not handled.

|                |      |            | Initialization in          |

|----------------|------|------------|----------------------------|

|                | AT   | mega25     | 560 (2/5)                  |

| Address Labels | Code |            | Comments                   |

| 0x000x0        | jmp  | RESET      | ; Reset Handler            |

| 0x0002         | jmp  | INT'O      | ; IRQO Handler             |

| 0x0004         | jmp  | INT'1      | ; IRQ1 Handler             |

| 0x0006         | jmp  | INT2       | ; IRQ2 Handler             |

| 0x0008         | jmp  | INT3       | ; IRQ3 Handler             |

| 0x000A         | jmp  | INT4       | ; IRQ4 Handler             |

| 0x000C         | jmp  | INT5       | ; IRQ5 Handler             |

| 0x000E         | jmp  | INT6       | ; IRQ6 Handler             |

| 0x0010         | jmp  | INT7       | ; IRQ7 Handler             |

| 0x0012         | jmp  | PCINTO     | ; PCINTO Handler           |

| 0x0014         | jmp  | PCINT1     | ; PCINT1 Handler           |

| 0x0016         | jmp  | PCINT2     | ; PCINT2 Handler           |

| 0X0018         | jmp  | WDT        | ; Watchdog Timeout Handler |

| 0x001A         | jmp  | TIM2_COMPA | ; Timer2 CompareA Handler  |

| 0x001C         | jmp  | TIM2 COMPB | ; Timer2 CompareB Handler  |

| <b>Interrupt Vector Initialization in</b> |

|-------------------------------------------|

| ATmega2560 (3/5)                          |

| 0x001E | jmp | TIM2_OVF    | ; Timer2 Overflow Handler         |

|--------|-----|-------------|-----------------------------------|

| 0x0020 | jmp | TIM1_CAPT   | ; Timer1 Capture Handler          |

| 0x0022 | jmp | TIM1_COMPA  | ; Timer1 CompareA Handler         |

| 0x0024 | jmp | TIM1_COMPB  | ; Timer1 CompareB Handler         |

| 0x0026 | jmp | TIM1_COMPC  | ; Timer1 CompareC Handler         |

| 0x0028 | jmp | TIM1_OVF    | ; Timer1 Overflow Handler         |

| 0x002A | jmp | TIMO_COMPA  | ; Timer0 CompareA Handler         |

| 0x002C | jmp | TIMO_COMPB  | ; Timer0 CompareB Handler         |

| 0x002E | jmp | TIMO_OVF    | ; Timer0 Overflow Handler         |

| 0x0030 | jmp | SPI_STC     | ; SPI Transfer Complete Handler   |

| 0x0032 | jmp | USART0_RXC  | ; USARTO RX Complete Handler      |

| 0x0034 | jmp | USARTO_UDRE | ; USARTO, UDR Empty Handler       |

| 0x0036 | jmp | USARTO_TXC  | ; USARTO TX Complete Handler      |

| 0x0038 | jmp | ANA_COMP    | ; Analog Comparator Handler       |

| 0x003A | jmp | ADC         | ; ADC Conversion Complete Handler |

| 0x003C | jmp | EE_RDY      | ; EEPROM Ready Handler            |

| 0x003E | jmp | TIM3_CAPT   | 7 Timer3 Capture Handler          |

|        |     |             |                                   |

|        | Ā   | Tmogo       | 2560 (1/5)                   |

|--------|-----|-------------|------------------------------|

|        | A   | Intega      | 2560 (4/5)                   |

| 0x0040 | jmp | TIM3_COMPA  | ; Timer3 CompareA Handler    |

| 0x0042 | jmp | TIM3_COMPB  | ; Timer3 CompareB Handler    |

| 0x0044 | jmp | TIM3_COMPC  | ; Timer3 CompareC Handler    |

| 0x0046 | jmp | TIM3_OVF    | ; Timer3 Overflow Handler    |

| 0x0048 | jmp | USART1_RXC  | ; USART1 RX Complete Handler |

| 0x004A | jmp | USART1_UDRE | ; USART1, UDR Empty Handler  |

| 0x004C | jmp | USART1_TXC  | ; USART1 TX Complete Handler |

| 0x004E | jmp | IWI         | ; 2-wire Serial Handler      |

| 0x0050 | jmp | SPM_RDY     | ; SPM Ready Handler          |

| 0x0052 | jmp | TIM4_CAPT   | ; Tîmer4 Capture Handler     |

| 0x0054 | jmp | TIM4_COMPA  | ; Timer4 CompareA Handler    |

| 0x0056 | jmp | TIM4_COMPB  | ; Timer4 CompareB Handler    |

| 0x0058 | jmp | TIM4_COMPC  | ; Timer4 CompareC Handler    |

| 0x005A | jmp | TIM4_OVF    | ; Timer4 Overflow Handler    |

| 0x005C | jmp | TIM5 CAPT   | ; Timer5 Capture Handler     |

| <b>Interrupt Vector Initialization in</b> |

|-------------------------------------------|

| ATmega2560 (5/5)                          |

| 0x0060        | jmp             | TIM5_COMPB        | ; Timer5 CompareB Handler         |

|---------------|-----------------|-------------------|-----------------------------------|

| 0x0062        | jmp             | TIM5_COMPC        | ; Timer5 CompareC Handler         |

| 0x0064        | jmp             | TIM5_OVF          | ; Timer5 Overflow Handler         |

| 0x0066        | jmp             | USART2_RXC        | ; USART2 RX Complete Handler      |

| 0x0068        | jmp             | USART2_UDRE       | ; USART2,UDR Empty Handler        |

| 0x006A        | jmp             | USART2_TXC        | ; USART2 TX Complete Handler      |

| 0x006C        | jmp             | USART3_RXC        | ; USART3 RX Complete Handler      |

| 0x006E        | jmp             | USART3_UDRE       | ; USART3,UDR Empty Handler        |

| 0x0070        | jmp             | USART3_TXC        | ; USART3 TX Complete Handler      |

| 1             |                 |                   |                                   |

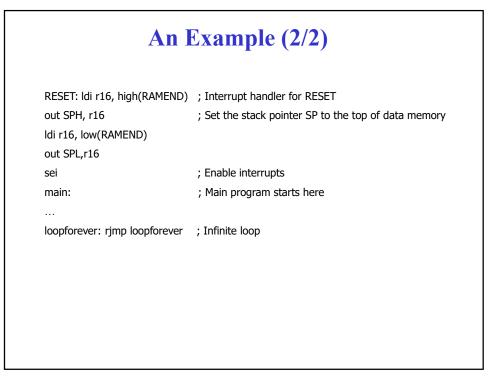

| 0x0072 RESET: | ldi             | r16, high(RAMEND) | ; Main program start              |

| 0x0073        | out             | SPH,r16           | ; Set Stack Pointer to top of RAM |

| 0x0074        | ldi             | r16, low(RAMEND)  |                                   |

| 0x0075        | out             | SPL,r16           |                                   |

| 0x0076        | sei             |                   | ; Enable interrupts               |

| 0x0077        | <instr></instr> | XXX               |                                   |

|               |                 |                   |                                   |

| An Example (1/2)                                                        |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| .include "m2560def.inc"                                                 |  |  |  |  |  |  |  |

| .cseg                                                                   |  |  |  |  |  |  |  |

| .org 0x0000 ; Reset vector is at address 0x0000                         |  |  |  |  |  |  |  |

| jmp RESET ; Jump to the start of Reset interrupt handler                |  |  |  |  |  |  |  |

| .org INT0addr ; INT0addr is the address of INT0 defined in m2560def.inc |  |  |  |  |  |  |  |

| jmp IRQ0 ; Jump to the start of the interrupt handler of IRQ0           |  |  |  |  |  |  |  |

| .org INT1addr ; INT1addr is the address of INT1 defined in m2560def.inc |  |  |  |  |  |  |  |

| reti ; Return to the breakpoint where INT1 occurred                     |  |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |  |

| .org 0x0072 ; Next instruction start at 0x0072                          |  |  |  |  |  |  |  |

| IRQ0: push r0 ; Save r0                                                 |  |  |  |  |  |  |  |

| push r1 ; Save r1                                                       |  |  |  |  |  |  |  |

| ; Body of the interrupt handler of INT0                                 |  |  |  |  |  |  |  |

| pop r1 ; Restore r1                                                     |  |  |  |  |  |  |  |

| pop r0 ; Restore r0                                                     |  |  |  |  |  |  |  |

| reti ; Return to the breakpoint where INT0 occurred                     |  |  |  |  |  |  |  |

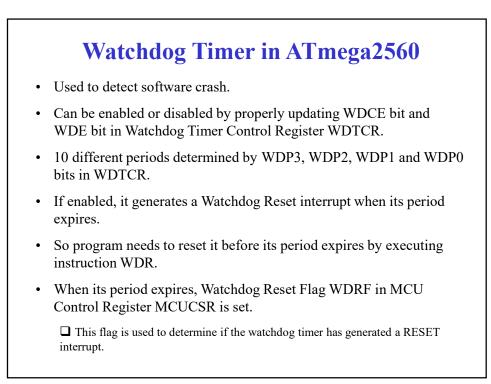

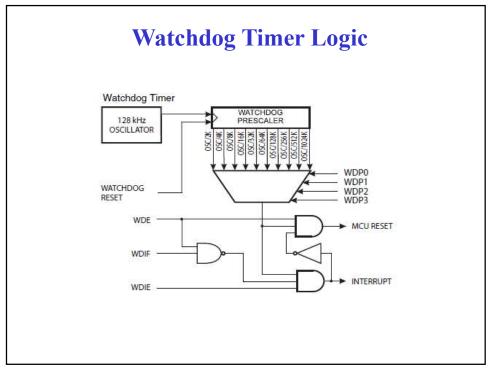

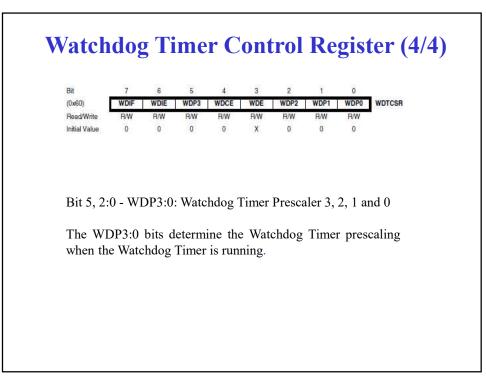

| Table 12 |      |      |      | og Timer P                         | eriou                                         |

|----------|------|------|------|------------------------------------|-----------------------------------------------|

| WDP3     | WDP2 | WDP1 | WDP0 | Number of WDT Oscillator<br>Cycles | Typical Time-out at<br>V <sub>CC</sub> = 5.0V |

| 0        | 0    | 0    | 0    | 2K (2048) cycles                   | 16ms                                          |

| 0        | 0    | 0    | 1    | 4K (4096) cycles                   | 32ms                                          |

| 0        | 0    | 1    | 0    | 8K (8192) cycles                   | 64ms                                          |

| 0        | 0    | 1    | 1    | 16K (16384) cycles                 | 0.125s                                        |

| 0        | 1    | 0    | 0    | 32K (32768) cycles                 | 0.25s                                         |

| 0        | 1    | 0    | 1    | 64K (65536) cycles                 | 0.5s                                          |

| 0        | 1    | 1    | 0    | 128K (131072) cycles               | 1.0s                                          |

| 0        | 1    | 1    | 1    | 256K (262144) cycles               | 2.0s                                          |

| 1        | 0    | 0    | 0    | 512K (524288) cycles               | 4.0s                                          |

| 1        | 0    | 0    | 1    | 1024K (1048576) cycles             | 8.0s                                          |

| 1        | 0    | 1    | 0    |                                    |                                               |

| 1        | 0    | 1    | 1    | Reserved                           |                                               |

| 1        | 1    | 0    | 0    |                                    |                                               |

| 1        | 1    | 0    | 1    |                                    |                                               |

| 1        | 1    | 1    | 0    |                                    |                                               |

| 1        | 1    | 1    | 1    |                                    |                                               |

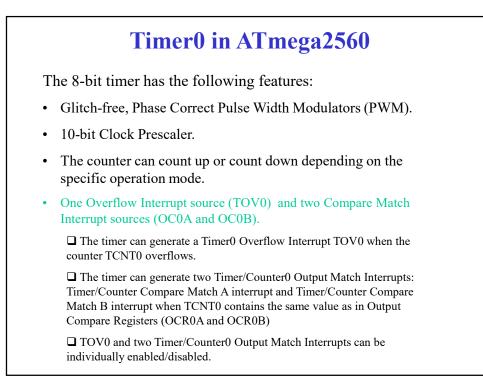

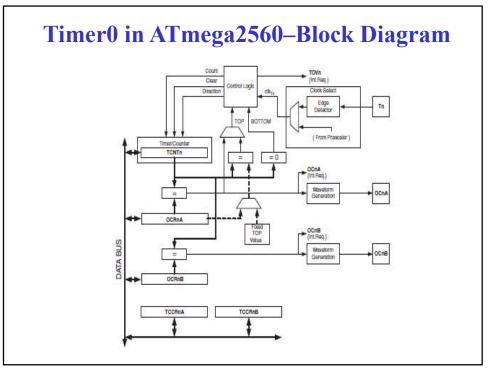

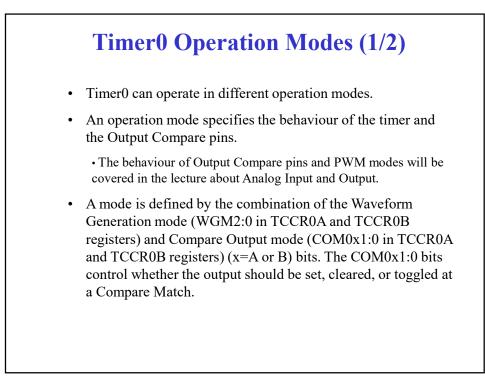

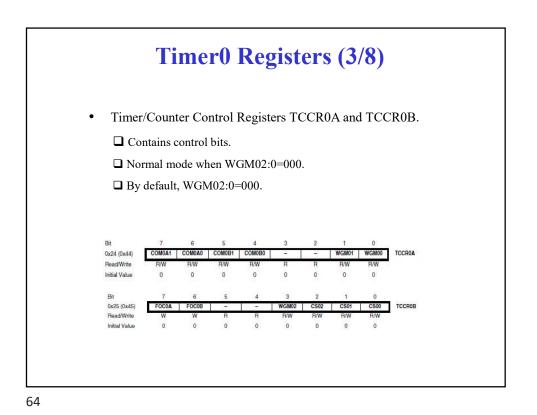

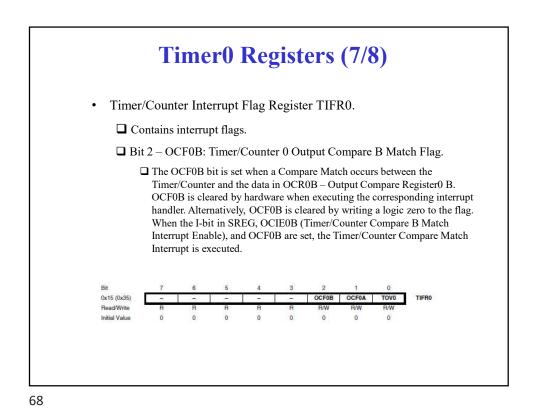

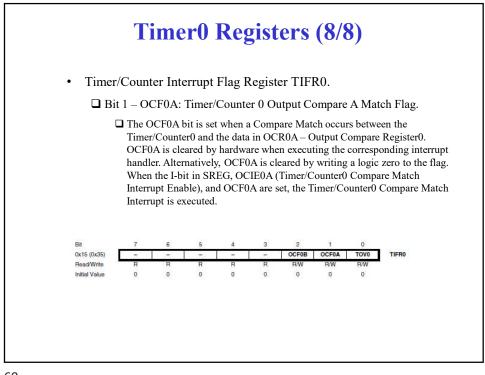

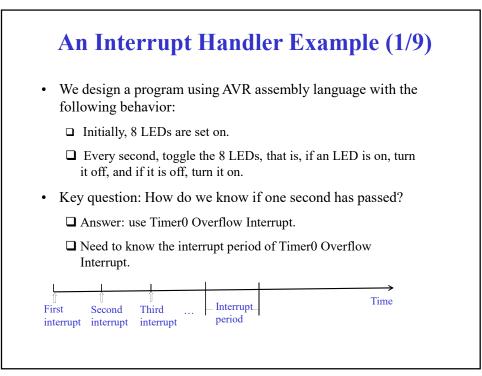

#### **Timer0 Operation Modes (2/2)**

- The simplest operation mode is the normal mode (WGM02:0 = 000 in TCCR0A and TCCR0B registers), which is typically used to generate an interrupt, either a Timer Overflow Interrupt, or a Compare Match Interrupt.

- In the normal mode, the counting direction is always up (incrementing). The counter simply overruns when it passes its maximum 8-bit value 0xFF and then restarts from 0x00.

<sup>□</sup> We focus on the normal mode now, and will learn the other modes in the lecture about Analog Input and Output.

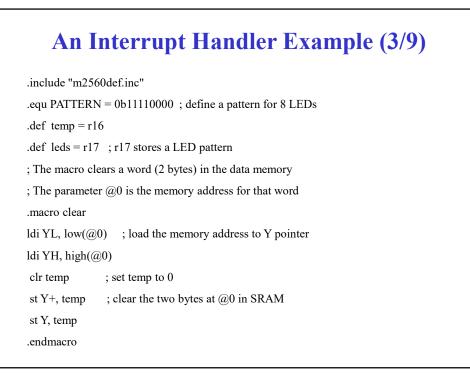

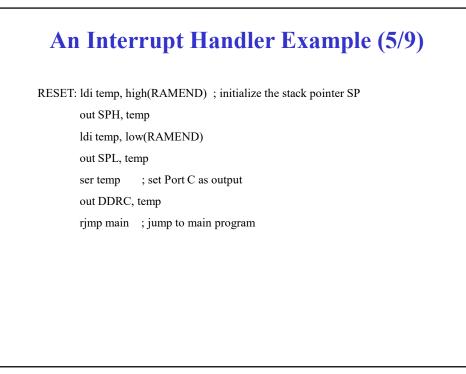

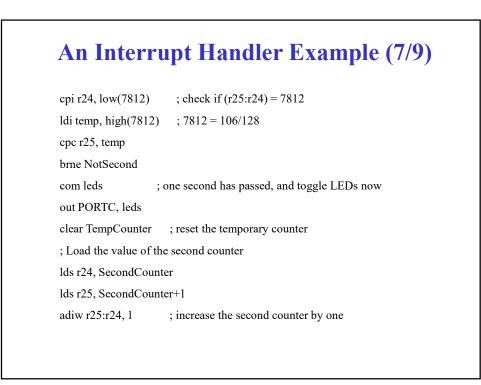

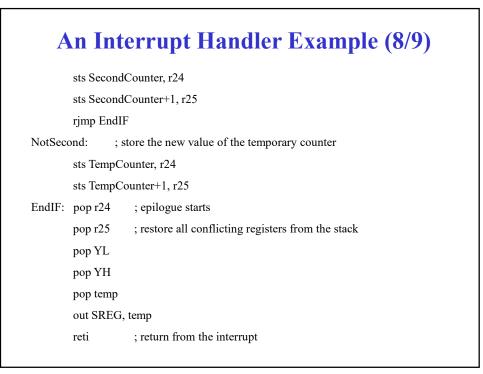

## An Interrupt Handler Example (4/9)

```

.dseg

SecondCounter: .byte 2 ; two-byte counter for counting seconds.

TempCounter: .byte 2

; temporary counter used to determine if one second has passed

.cseg

.org 0x0000

jmp RESET

; no handling for IRQ0.

jmp DEFAULT

jmp DEFAULT

; no handling for IRQ1.

.org OVF0addr

; OVF0addr is the address of Timer0 Overflow Interrupt Vector

jmp Timer0OVF ; jump to the interrupt handler for Timer0 overflow.

...

jmp DEFAULT

; default service for all other interrupts.

DEFAULT: reti

; no interrupt handling

```

| An Interrupt Handler Example (6/9)                       |

|----------------------------------------------------------|

| Timer0OVF: ; interrupt subroutine to Timer0              |

| in temp, SREG                                            |

| push temp ; prologue starts                              |

| push YH ; save all conflicting registers in the prologue |

| push YL                                                  |

| push r25                                                 |

| push r24 ; prologue ends                                 |

| ; Load the value of the temporary counter                |

| lds r24, TempCounter                                     |

| lds r25, TempCounter+1                                   |

| adiw r25:r24, 1 ; increase the temporary counter by one  |

|                                                          |

|                                                          |

| An Interru                                                                                 | ot Handler Example (9/9)                      |

|--------------------------------------------------------------------------------------------|-----------------------------------------------|

| ain: ldi leds, 0xFF ; m                                                                    | ain program starts here                       |

| out PORTC, leds ; se                                                                       | t all LEDs on at the beginning                |

| ldi leds, PATTERN                                                                          |                                               |

| clear TempCounter                                                                          | ; initialize the temporary counter to 0       |

| clear SecondCounter                                                                        | ; initialize the second counter to 0          |

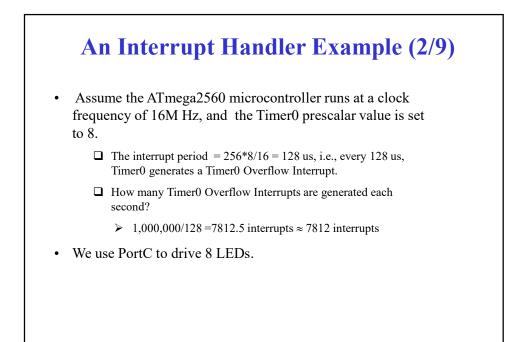

| ldi temp, 0b0000000                                                                        |                                               |

| out TCCR0A, temp                                                                           |                                               |

| ldi temp, 0b0000010                                                                        |                                               |

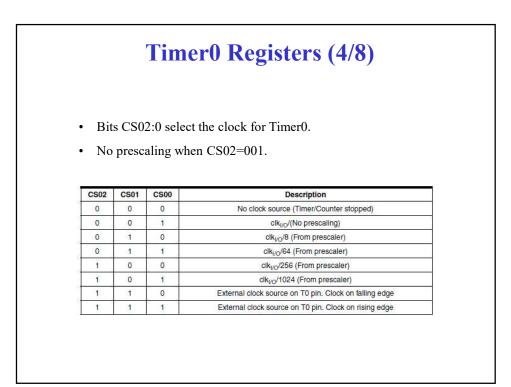

| out TCCR0B, temp                                                                           | ; set prescalar value to 8                    |

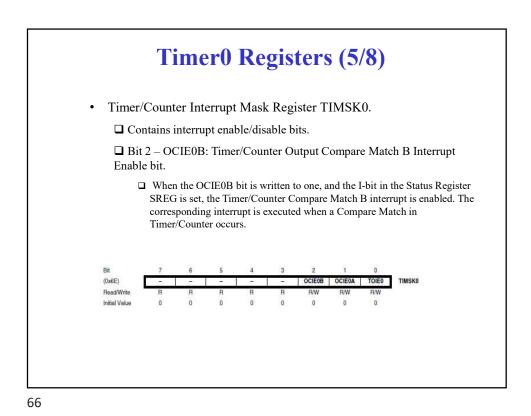

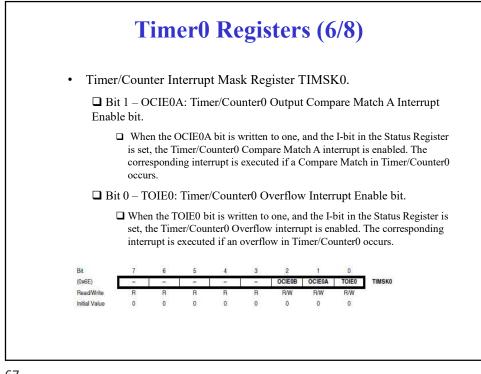

| ldi temp, 1< <toie0< td=""><td>; TOIE0 is the bit number of TOIE0 which is 0</td></toie0<> | ; TOIE0 is the bit number of TOIE0 which is 0 |

| sts TIMSK0, temp                                                                           | ; enable Timer0 Overflow Interrupt            |

| sei                                                                                        | ; enable global interrupt                     |

| loop: rjmp loop ; loo                                                                      | pp forever                                    |

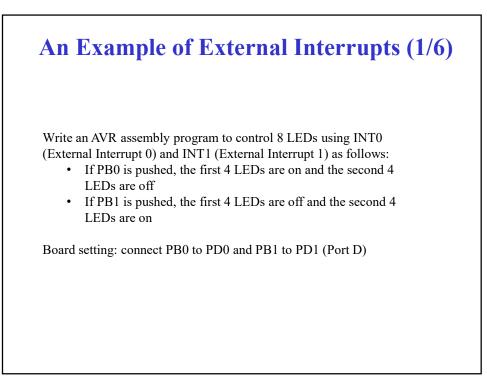

## An Example of External Interrupts (2/6)

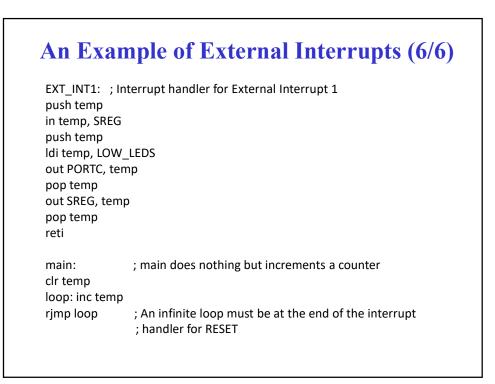

.include "m2560def.inc" .def temp =r16 .equ HIGH\_LEDS = 0b11110000 .equ LOW\_LEDS = 0b00001111 .cseg .org 0x0 jmp RESET ; interrupt vector for RESET .org INT0addr ; INT0addr is the address of EXT\_INT0 ; (External Interrupt 0) jmp EXT\_INT0 ; interrupt vector for External Interrupt 0 .org INT1addr ; INT1addr is the address of EXT\_INT1 ; (External Interrupt 1) jmp EXT\_INT1 ; interrupt vector for External Interrupt 1