# 21 General-purpose timers (TIM2/TIM3/TIM4)

#### 21.1 TIM2/TIM3/TIM4 introduction

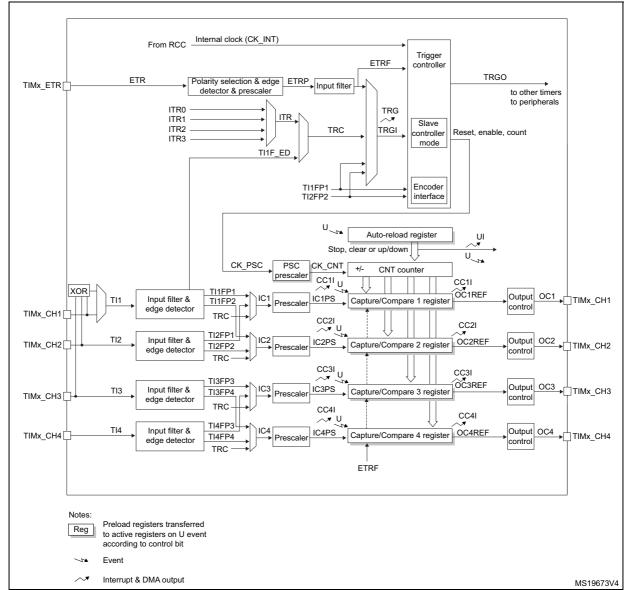

The general-purpose timers consist of a 16-bit/32-bit auto-reload counter driven by a programmable prescaler.

They may be used for a variety of purposes, including measuring the pulse lengths of input signals (*input capture*) or generating output waveforms (*output compare and PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the RCC clock controller prescalers.

The timers are completely independent, and do not share any resources. They can be synchronized together as described in *Section 21.3.19: Timer synchronization*.

Note:

TIM4 is available only on STM32F303xB/C/D/E, STM32F358xC and STM32F398xE devices.

### 21.2 TIM2/TIM3/TIM4 main features

General-purpose TIMx timer features include:

- 16-bit (TIM3 and TIM4) or 32-bit (TIM2) up, down, up/down auto-reload counter.

- 16-bit programmable prescaler used to divide (also "on the fly") the counter clock frequency by any factor between 1 and 65535.

- Up to 4 independent channels for:

- Input capture

- Output compare

- PWM generation (Edge- and Center-aligned modes)

- One-pulse mode output

- Synchronization circuit to control the timer with external signals and to interconnect several timers.

- Interrupt/DMA generation on the following events:

- Update: counter overflow/underflow, counter initialization (by software or internal/external trigger)

- Trigger event (counter start, stop, initialization or count by internal/external trigger)

- Input capture

- Output compare

- Supports incremental (quadrature) encoder and hall-sensor circuitry for positioning purposes

- Trigger input for external clock or cycle-by-cycle current management

608/1148 RM0316 Rev 10

Figure 197. General-purpose timer block diagram

5

RM0316 Rev 10 609/1148

# 22 Basic timers (TIM6/TIM7)

### 22.1 TIM6/TIM7 introduction

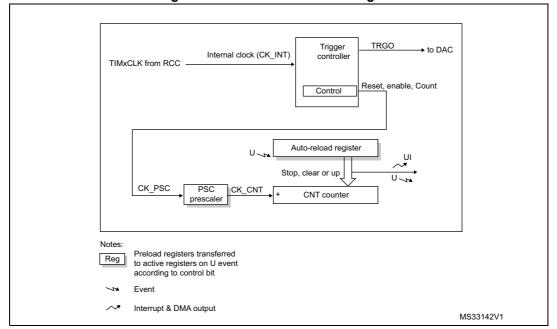

The basic timers TIM6 and TIM7 consist of a 16-bit auto-reload counter driven by a programmable prescaler.

They may be used as generic timers for time base generation but they are also specifically used to drive the digital-to-analog converter (DAC). In fact, the timers are internally connected to the DAC and are able to drive it through their trigger outputs.

The timers are completely independent, and do not share any resources.

### 22.2 TIM6/TIM7 main features

Basic timer (TIM6/TIM7) features include:

- 16-bit auto-reload upcounter

- 16-bit programmable prescaler used to divide (also "on the fly") the counter clock frequency by any factor between 1 and 65535

- Synchronization circuit to trigger the DAC

- Interrupt/DMA generation on the update event: counter overflow

Figure 247. Basic timer block diagram

678/1148 RM0316 Rev 10

## 22.3 TIM6/TIM7 functional description

#### 22.3.1 Time-base unit

The main block of the programmable timer is a 16-bit upcounter with its related auto-reload register. The counter clock can be divided by a prescaler.

The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running.

The time-base unit includes:

- Counter Register (TIMx CNT)

- Prescaler Register (TIMx PSC)

- Auto-Reload Register (TIMx ARR)

The auto-reload register is preloaded. The preload register is accessed each time an attempt is made to write or read the auto-reload register. The contents of the preload register are transferred into the shadow register permanently or at each update event UEV, depending on the auto-reload preload enable bit (ARPE) in the TIMx\_CR1 register. The update event is sent when the counter reaches the overflow value and if the UDIS bit equals 0 in the TIMx\_CR1 register. It can also be generated by software. The generation of the update event is described in detail for each configuration.

The counter is clocked by the prescaler output CK\_CNT, which is enabled only when the counter enable bit (CEN) in the TIMx CR1 register is set.

Note that the actual counter enable signal CNT EN is set 1 clock cycle after CEN.

### **Prescaler description**

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It is based on a 16-bit counter controlled through a 16-bit register (in the TIMx\_PSC register). It can be changed on the fly as the TIMx\_PSC control register is buffered. The new prescaler ratio is taken into account at the next update event.

*Figure 248* and *Figure 249* give some examples of the counter behavior when the prescaler ratio is changed on the fly.