COMP3222 Notices

Notices

-

Final Exam Tomorrow

Posted by Oliver Diessel Wednesday 15 November 2017, 03:15:09 PM.

Reminder: The COMP3222/9222 exams are on tomorrow from 1:30pm - 5:45pm in the Brass, Sitar and Kora labs on Level 3 of J17 (Rooms J17-305, J17-306 and J17-307).

Please remember for tomorrow's exam that the virtual machine does not support USB3 devices directly - you will need to use a USB extension cable to connect a USB3 drive to the vm.

-

Lab marks recorded

Posted by Oliver Diessel Monday 30 October 2017, 03:12:38 PM.

Your lab marks have now been recorded in SMS. Please check these in the usual way and let your lab demonstrator know if there are any discrepancies.

-

Hand In marks released

Posted by Oliver Diessel Monday 23 October 2017, 02:01:37 PM, last modified Monday 23 October 2017, 02:04:32 PM.

Marks for your Hand In exercises have been loaded into SMS - access these in the usual way - your marked Hand In exercises will be returned during this week's tutorials. Lab marks will be entered into SMS by Friday afternoon this week.

Reminder: this is Week 13 - last week for tutes and labs.

-

Practice practical exam

Posted by Oliver Diessel Monday 16 October 2017, 02:15:47 PM, last modified Monday 16 October 2017, 05:22:35 PM.

The Course Wrap-up and Practice Practical Exam are now available on the Course website under the Week 12 Lectures link..

The Practice Practical Exam solution will be covered during the last tutorial in Week 13.

Good luck with finishing off the labs and in the final exam!

-

Debugging VHDL

Posted by Oliver Diessel Tuesday 10 October 2017, 09:55:16 AM, last modified Tuesday 10 October 2017, 09:56:27 AM.

If you are having trouble figuring out why your PROCESS isn't working as expected, please take a look at Steve Wilton's lecture from last week, which has immeasurably sage advice on how to cut down your debug time: In the first instance, ensure that you can unequivocally categorise each process as being 1. purely combinational, 2. purely synchronous, or 3. synchronous, with an asynchronous reset. Secondly: ensure that you follow the specific rules for each type of process. By following these rules you are almost certainly going to have fewer bugs in the hardware generated from your description.

-

Tutes in Week 11 (next week)

Posted by Oliver Diessel Friday 06 October 2017, 04:35:14 PM.

As we missed out on tutorials this week, we will be covering the tutorial for Week 10 during tutorials next week.

In order to catch up, I will cover the Week 11 tutorial material (now posted) during the Thursday lecture next week (12/10).

-

Guest lecturer this Thursday: Prof Steve Wilton, University of British Columbia

Posted by Oliver Diessel Tuesday 03 October 2017, 01:04:53 PM.

Hi all,

We are extremely privileged to have Prof Steve Wilton from UBC on campus this Thursday and willing to give a guest lecture on "VHDL for Synthesis" to COMP3222/9222.

Steve Wilton is a Professor in the Department of Electrical and Computer Engineering at the University of British Columbia. His research focuses on the architectures of next-generation Field-Programmable Gate Arrays and their associated Computer-Aided Design Tools. Along with his students, he has investigated many areas related to Field-Programmable Technology, ranging from flexible memories, routing architectures, power-efficient architectures, packing, placement, and routing algorithms, analytical modeling and debugging techniques.

Please don't miss this opportunity to hear Steve if you can make it!

Oliver

-

No tutes in Week 10

Posted by Oliver Diessel Friday 22 September 2017, 04:25:30 PM.

Given we have a public holiday on Monday 2 October, I propose we cover the Week 10 tutorial contents during the tutorial in Week 11, and cover the Week 11 tutorial during the Thursday lecture hour in Week 11. We should thereafter be back on track with the usual tutorial schedule. The Tuesday 3 October tutorial will therefore be cancelled.

-

Hand in Exercises now available

Posted by Oliver Diessel Friday 22 September 2017, 04:08:29 PM, last modified Friday 22 September 2017, 04:09:54 PM.

Hi all,

The Hand in Exercises have now been released. Please note that they are due to be handed in at the start of the Monday lecture in Week 12 (October 16). Please arrange someone else to hand in your solution if you are unable to make it to that lecture.

Please also note that you are asked to confirm that your board works properly as one of the Hand in Exercises. This is to ensure your board works adequately for the final practical exam. Let your demonstrator know of any problems with your board.

Have a good break & see you on Thursday 5 October, when we expect to have Prof Steve Wilton, a famous FPGA designer from the University of British Columbia, give his lecture on VHDL for synthesis.

-

Grade availability from WebCMS3

Posted by Oliver Diessel Wednesday 30 August 2017, 10:33:12 AM, last modified Wednesday 30 August 2017, 10:34:25 AM.

Apparently, the connection to our CSE Student Management System (SMS) from WebCMS3 is currently down. Thus the little graph icon at the bottom of the menu to the left does not currently work.

In the meantime, you can access your marks via the command line from a CSE server using the command:

3222|9222 class run -sturec

or you can use the Give/SMS web interface:

https://cgi.cse.unsw.edu.au/~give/code/login.php?app=/~give/Student/sturec.php

The direct link between WebCMS3 and SMS should be back up within a day or so.

-

Lab results to date

Posted by Oliver Diessel Friday 25 August 2017, 03:10:39 PM.

Lab results we have recorded for you so far have now been uploaded. Access these via the 3222|9222 classrun -sturec command from your CSE login or via the grade (bar chart) symbol towards the bottom of the menu on the left.

-

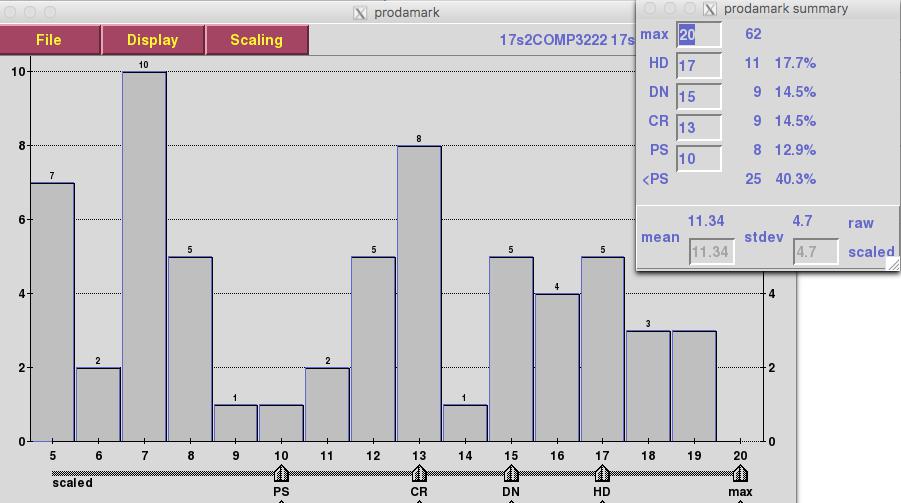

Quiz results

Posted by Oliver Diessel Wednesday 23 August 2017, 09:35:29 PM, last modified Thursday 24 August 2017, 09:32:05 AM.

Monday's quiz has been marked. You can retrieve your score by entering 3222 classrun -sturec if you are an undergrad, or 9222 classrun -sturec if you're a postgrad, at the UNIX prompt of your CSE home account.

The results are distributed as follows:

Clearly the quiz partitioned the class into two distinct groups - the 60% of the class that passed, and the 40% that did not. Given the number of people who scored very well (20/62 scored a distinction or above), I don't think this was a difficult quiz.

-

Quiz 1:15-2:15 pm, Monday 21 August

Posted by Oliver Diessel Wednesday 16 August 2017, 10:11:57 AM.

The COMP3222/9222 Quiz will be held from 1:15-2:15 pm during next Monday's lecture in the usual room.

The Quiz is closed book, and will potentially examine all course materials covered up until the end of Week 4.

Please arrive promptly so that we can start/finish on time.

-

Guest lecturer, Prof Donald Bailey, Thursday 10 August: Embedded Imaging Systems - The Case for FPGAs

Posted by Oliver Diessel Thursday 27 July 2017, 11:54:39 AM, last modified Thursday 27 July 2017, 07:13:19 PM.

We are fortunate to have Donald Bailey from the Image and Signal Processing Research Group at Massey University visit the COMP3222 class on 10/08 to give a talk on the use of FPGAs to implement embedded imaging systems.

Abstract: Vision is increasingly being embedded within devices and products. The trend for increasing resolution places considerable demands on the image processing, especially for small, low-power embedded systems. It is shown that Field Programmable Gate Array (FPGA) Technology is well suited to meet the computational demands of embedded imaging systems, especially for low-level image processing tasks. The differences between conventional software design and FPGA based design are outlined.

-

Welcome to Digital Circuits & Systems

Posted by Oliver Diessel Tuesday 04 July 2017, 03:34:23 PM.

Welcome to the 17s2 offering of COMP3222/9222 Digital Circuits & Systems!

The Course Outline will be updated shortly so please revisit this page before the start of session.